# User's Guide

Publication number E3485-97000 August 2001

For Safety information, Warranties, and Regulatory information, see the pages behind the index.

© Copyright Agilent Technologies 1994-2001 All Rights Reserved

Agilent Technologies E5904B Option 060 Trace Port Analyzer for IBM PowerPC 4XX

# Trace Port Analyzer —At a Glance

# **On-Chip Circuitry for Debugging**

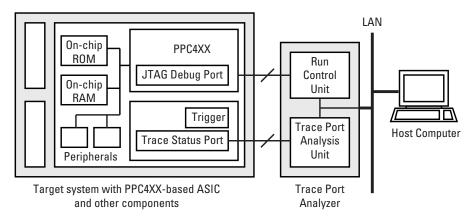

The PowerPC 400 family of microprocessors includes a trace port that outputs information about processor execution.

Software debuggers provide the user interface to the PowerPC 400 family processors; they configure the trace port using a run control unit (via the JTAG interface), and they display the data collected from the trace port.

# **Trace Port Analyzer Overview**

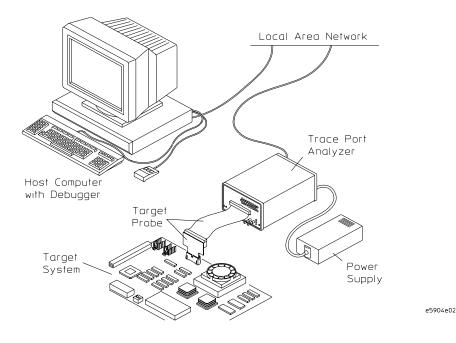

The Agilent Technologies E5904B Option 060 Trace Port Analyzer contains:

- A run control unit.

- Circuitry for collecting output from the trace port, called the trace port analysis unit.

- A LAN interface for communicating with debuggers.

### The Run Control Unit

In addition to configuring the trace port, the run control unit is also used for downloading code, starting/stopping processor execution, single-stepping through a program, setting breakpoints, and displaying/modifying registers and memory.

### The Trace Port Analysis Unit

With the trace port analysis unit, you can:

- Capture trace data.

- Store up to 4M trace states.

- Capture data on trace ports whose voltages are between 1.8V and 5.0V.

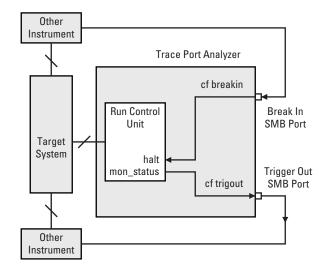

- Send a trigger signal or a run control unit status signal to other instruments, or use signals received from other test instruments to stop processor execution or trigger the trace port analyzer.

### The LAN Interface

With the IEEE 802.3 Type 10/100Base-TX LAN connection, you can:

- Connect the trace port analyzer to a target system in the lab and use debuggers anywhere else on the LAN.

- Connect to either 10 Mbps (10BASE-T) or 100 Mbps (100BASE-TX) twisted-pair ethernet LANs. (The trace port analyzer automatically negotiates the data rate for the LAN it is connected to.)

### **Debugger Software**

A debugger must be used with the trace port analyzer. Debuggers such as RISCWatch from IBM, SingleStep from WindRiver, and others can be used.

The debugger user interface will let you:

- Download code, start/stop processor execution, single-step through a program, set breakpoints, and display/modify registers and memory.

- Set triggers, trigger sequences, etc. using the run control unit of the trace port analyzer.

- Collect trace information.

- Display execution flow and captured trace data.

# **Processors and ASIC Cores Supported**

The Agilent Technologies E5904 Option 060 Trace Port Analyzer supports the following processors and ASIC cores with JTAG run control. Trace support is as listed below.

| Processor | Trace Status Port                            |

|-----------|----------------------------------------------|

| NPe405    | Clock plus 8 trace status lines              |

| 440GP     | Clock plus 15 trace status lines             |

| 405CR     | Clock plus 8 trace status lines <sup>1</sup> |

| 405GP     | Clock plus 8 trace status lines <sup>1</sup> |

| 403GCX    | Clock plus 7 trace status lines              |

| 401GF     | JTAG debug port only                         |

| 403GA     | Clock plus 7 trace status lines              |

| 403GB     | JTAG debug port only                         |

| 403GC     | Clock plus 7 trace status lines              |

<sup>1</sup>GPIO pins 1-9 are used for both IO and trace.

| Core  | Trace Status Port                |

|-------|----------------------------------|

| 401x2 | Clock plus 6 trace status lines  |

| 401A1 | JTAG debug port only             |

| 405   | Clock plus 8 trace status lines  |

| 440   | Clock plus 15 trace status lines |

# **Equipment Supplied**

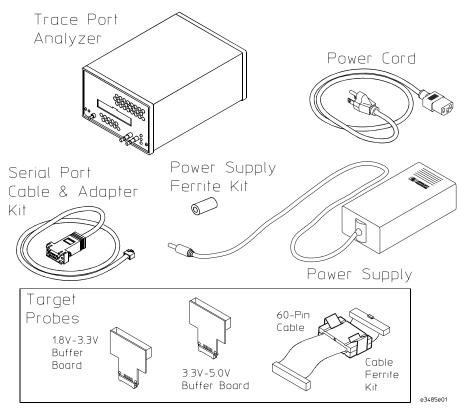

The Agilent Technologies E5904B Option 060 Trace Port Analyzer consists of:

| Part number | Description                                          |

|-------------|------------------------------------------------------|

| 0950-3043   | Power supply for trace port analyzer (marked F1044B) |

| E3483-68700 | Ferrite kit for power supply                         |

| E5903-61601 | 60-pin cable                                         |

| E3483-68700 | Ferrite kit for 60-pin cable                         |

| E5903-66503 | 1.8 V - 3.3 V buffer board                           |

| E5903-66502 | 3.3 V - 5.0 V buffer board                           |

| E8130-68702 | Serial cable and adapter                             |

| E3485-97000 | This user's guide                                    |

# In This Book

This is the User's Guide for the Agilent Technologies E5904B Option 060 Trace Port Analyzer. It describes:

- Target system design considerations and other requirements of the trace port analyzer.

- How to connect the trace port analyzer to a LAN, configure it, and connect it to the target system.

- How to coordinate measurements between the trace port analyzer and other test instruments.

- How to update trace port analyzer firmware.

- How to troubleshoot and solve problems.

- Characteristics of the trace port analyzer.

**See Also** For information regarding the use of your debugger, see the user's guide manual supplied with your debugger.

#### Trace Port Analyzer —At a Glance

Trace Port Analyzer Overview 2 Processors and ASIC Cores Supported 4 Equipment Supplied 5

#### In This Book

#### **1** Target System Design Considerations

Trace Port Signal Overview 15

ASIC Design Guidelines 17 ASIC Pad Selection and Placement 17

Printed-Circuit Board Design Guidelines 18 Trace Port 18

Header Connector Requirements 21 Recommended Orientation 21 Connector and Support Shroud Part Numbers 22 Connector Dimensions 23 Support Shroud Dimensions 24

Height Restrictions and Keep-Out Requirements 25 Target Header Connector Pin-Outs 28

Timing and Voltage Specifications for Trace Port Signals 30 Signal Requirements 30 Required Voltage Levels: 1.8 V - 3.3 V Buffer Board 31 Required Voltage Levels: 3.3 V - 5.5 V Buffer Board 32

Loading Effects 33 Target Probe Equivalent Load 34 Modeling the Trace Port Analyzer Buffer Board 35 Simplified Buffer Board Model 36

#### 2 Connecting to a Power Source

To connect the power supply 38 To turn power ON 40 To turn power OFF 40

#### **3** Connecting to a LAN

Step 1. Decide on the LAN setup method 43

What is DHCP? 43

How does the trace port analyzer use DHCP? 43

How does DHCP interact with other methods of setting LAN parameters? 43

Step 2. Set the trace port analyzer's LAN parameters 44 To set LAN parameters using DHCP 44 To set LAN parameters using a serial port connection 45 If there are serial port connection problems 50

Step 3. Connect the LAN cable 51

Step 4. Cycle power on the trace port analyzer 52

#### 4 Entering Commands

Establishing Communications over the LAN 55 To use debugger software 55 If the debugger cannot communicate with the trace port analyzer 55 To "telnet" to the trace port analyzer 56 If you cannot "telnet" to the trace port analyzer 57

Using the Trace Port Analyzer's Built-In Commands 58 Command Prompts 58 Commonly Used Commands 59 Online Help 60

#### **5** Configuring the Trace Port Analyzer

Using the Built-In "cf" Command 63

Setting the Configuration Options 65 To specify whether runs are restricted to real-time 65 To specify the reset behavior 66 To specify the JTAG clock speed 67 To set the freeze timers option 69 To enable or disable address validation 70 To configure the memory read operation 71 To configure data memory write operations 72 To configure instruction memory write operations -74 To enable branch folding 76 To configure the Break In SMB port 77 To configure the Trigger Out SMB port 78 To enable fast memory loads 79 To configure the voltage reference 80 To configure the threshold voltage 81 To configure the autostop mode 82 To save and restore configuration option settings 83

#### 6 Connecting to a Target System

Connecting the Trace Port Analyzer to the Target System 87

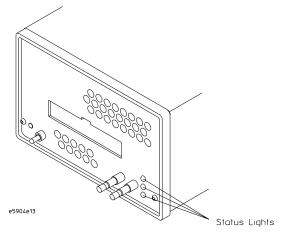

Verifying the Target System Connection 90 To verify trace port analyzer operation 90 If the trace port analyzer doesn't work with the debugger 90 If there are target system interaction problems 90

#### 7 Coordinating Measurements with Other Test Instruments

Receiving a Break In Signal from Another Test Instrument 94 To halt processor execution 94

Driving a Trigger Out Signal to Another Test Instrument 95 To indicate when processor execution stops 95

#### 8 Updating Firmware

To display current firmware version information 98 To get firmware from the web 98 To update firmware from a floppy disk 99

#### 9 Solving Problems

Interpreting the Trace Port Analyzer Status Lights 103 Power ON Light 103 LAN Status Lights 104 Target System Status Lights 105

Verifying Trace Port Analyzer LAN Communications 106 Step 1. Verify the physical connection 106 Step 2. Use the "ping" command on a networked computer 106 If there are LAN connection problems 107 If it takes a long time to connect to the network 108

Checking the Initial Trace Port Analyzer Status 109 If the prompt is "->" 109 If the prompt is "?>" 110

Verifying Run Control Interaction with the Target System 111 Step 1. Initialize the trace port analyzer 111 If the response is "!ERROR 905!" 112 If the initial prompt is "p>" 112If the initial prompt is "M>" 112If the initial prompt is ">" 113 Step 2. Configure the trace port analyzer 113 Step 3. Enter the reset command 114 Step 4. Enter the run command 114 Step 5. Enter the break command 114 If the prompt is "U>" with error messages 115 115Step 6. Check register and memory access If you see memory-related problems 116 Step 7. Run a short program 116 If the program does not execute correctly 117 If the trace port analyzer has problems controlling the target system 118

Contacting Agilent Technologies 120

#### **10** Characteristics

Input/Output Electrical Characteristics 123 Trigger Out SMB Port 123 Break In SMB Port 123 Communication Ports 123 Power Supply 123

Run Control Unit Characteristics 124 Processor Compatibility 124 Electrical Characteristics 124 Output Model 125

Trace Port Analysis Unit Characteristics 126

Environmental Characteristics 127

#### 11 Service Guide

To get replacement parts 130 To exchange a faulty assembly for a repaired and tested assembly 130 To return a part to Agilent Technologies for service 131 To clean the instrument 131

#### Glossary

Index

Target System Design Considerations

The quality and timing of the trace port signals to the trace port analyzer are critical for reliable operation. Some of the ASIC and printed-circuit board design issues to consider are:

- Output pad selection.

- Printed-circuit board trace lengths.

- Printed-circuit board trace termination.

- Setup and hold times for the trace data signals with respect to the trace clock.

The care that must be taken with the design of the trace port is generally proportional to the frequency of operation. At frequencies of more than 100 MHz careful SPICE analysis of the system, including the characteristics of the package should ideally be taken into account.

Early attention to the design guidelines can ensure correct operation of the trace port analyzer.

This chapter describes:

- Overview of signals

- A few ASIC design guidelines. More ASIC design guidelines may be available from the processor/core manufacturer.

- Printed-circuit board design guidelines.

- The header connector

- Height restrictions and keep-out requirements.

- Timing and voltage specifications for trace port signals.

- Header connector pinouts

- Buffer board voltage level requirements

- Buffer board modeling information

# Trace Port Signal Overview

The trace port signals are described below.

**TrcClk.** Trace clock generated by the target processor.

**TS[], ES[], BS[], and D0.** These are trace status signals output from the processor or ASIC. See IBM's PowerPC 4XX user's guide for details.

**VTRef.** The VTRef signal is intended to supply a logic-level reference voltage to allow debug equipment to adapt to the signaling levels of the target board.

Outputs to target systems will be clamped at VTRef on high level outputs. Inputs from the target system will be sensed in reference to the VTRef voltage level.

**NOTE:** VTRef does NOT supply operating current to the debug equipment.

Target boards should supply a voltage that is between 1.8 V and 5.0 V. The target board should provide a sufficiently low DC output impedance that the output voltage not change by more than 1% when supplying a nominal signal current  $\pm 0.4$  mA).

Debug equipment that connects to this signal should interpret it as a signal rather than a power supply pin and not load it more heavily than a signal pin. The recommended maximum source or sink current is  $\pm 0.4$ mA.

### Signals for JTAG control

The following signals are required for JTAG (IEEE 1149.1 test access port) control.

**nTRST.** The nTRST signal is actively driven by the trace port analyzer to the Reset signal on the target JTAG port.

**TDI.** TDI is the Test Data In signal from the run control unit to the target JTAG port. It is recommended that this pin is pulled to a defined state.

**TMS.** TMS is the Test Mode Select signal from the run control unit to the target JTAG port. This pin must be pulled up on the target system to prevent the TAP (Test Access Port) state machine from exiting (TLR) test logic reset mode when the trace port analyzer is not connected to the target system.

Chapter 1: Target System Design Considerations Trace Port Signal Overview

**TCK.** TCK is the Test Clock signal from the run control unit to the target JTAG port. It is recommended that this pin is pulled to a defined state.

**TDO.** TDO is the Test Data Out from the target JTAG port to the run control unit.

### **Signals for Processor Control**

**SRESET.** This is an open collector output from the run control unit to the target system reset. This is also an input to the run control unit so that a reset initiated on the target may be reported to the debugger.

This pin should be pulled up on the target to avoid unintentional resets when there is no connection.

**HALT.** This is an output from the run control unit to the target system. Active low.

# ASIC Design Guidelines

# **ASIC Pad Selection and Placement**

The position and type of pad selected is based on the following factors:

- Minimizing noise and coupling between trace and other signals.

- Ability to drive the external load.

It has been shown that the quality of the trace clock signal, as observed by the trace port analyzer, has the greatest effect on the reliability of the system. This is because it is vital that trace clock transition move cleanly through the threshold region of the input circuitry of the trace port analyzer, without glitches or ringing.

It has been observed that with certain types of package and pin placement the signal coupling between the trace data signals and the trace clock can be significant. If this is observed to be a problem during simulations, it is recommended that ground or static I/O signals are placed on both sides of the trace clock signal.

Contact the processor/core manufacturer for more ASIC design considerations.

# Printed-Circuit Board Design Guidelines

Two cases need to be considered:

- A dedicated trace port. The trace port analyzer is the only load on the trace port signals.

- A shared trace port. The trace pins are shared with other functions; therefore, there are stubs on the printed-circuit board traces of the development board, and there is an increased load on the output driver.

# **Trace Port**

Signal integrity at the trace port analyzer connector is very important. If you know the characteristics of your printed-circuit board traces, use the actual trace impedance and propagation delay.

If you do not have access to this information, a rough rule of thumb for microstrip (trace on outer layer over a ground plane) on FR4 printed-circuit board is a propagation speed of 63 ps/cm (160 ps/inch). The impedance of a 0.127 mm (0.005) inch wide trace as a microstrip is from 70 to 75 Ohms on a typical six-layer foil construction board. The impedance of a trace goes down as the width of the trace increases.

Knowledge of the characteristic impedance and signal edge rates of the target processor's or ASIC's trace port output drivers is necessary for proper design of the target system. Signals must be carefully routed from the target processor or ASIC to the trace port connector using high-speed design practices including using termination when necessary.

Also required is the actual setup and hold provided by the ASIC trace port outputs with reference to the trace clock. If you do not know the characteristics of the signals from your ASIC, consult your ASIC vendor. The variation between ASIC vendors on trace port output drivers and timing make it difficult to provide any general rule.

The output drive model for the Agilent trace port analyzer is provided in "Output Model" on page 125.

### **Printed-Circuit Board trace Length**

Match all TS, ES, D0, BS, and TrcClk trace lengths between the processor or ASIC and the trace port connector within 100 ps. Overall differences of greater than 100 ps in trace lengths directly impact setup and hold requirements. If TrcClk is delayed compared to the data, the setup specification needs to be increased by the additional delay. If any data is delayed compared to the clock, the additional delay needs to be added to the setup requirement. If data paths are such that data has both greater than and less than delays compared with the clock, the difference needs to be added to both the setup and hold specification.

### Signal Quality

Reflections, overshoot, and undershoot all need to be minimized to ensure accurate data acquisition. The primary variable is the rise time of a signal compared to its trace length. This is where the minimum signal rise and fall time becomes important.

The following points should be considered:

- 1. Ensure the one way propagation time for all traces is less than 1/3 of the signal rise time.

- 2. If traces must be longer than 1/3 of the signal rise time, then some form of signal termination is required. The recommended method is series termination. The series resistor must be placed as close as possible to the ASIC pin. The value of this series resistor, when added to the output impedance of the signal driver should closely match the impedance of the printed-circuit board trace. Certain processors include a series resistor in the trace output buffer—see the processor manufacturer's user's guide for details of processor output driver characteristics.

- 3. If series termination cannot be used, add parallel or matched AC termination on each signal trace at the trace port analyzer target header connector. This requires significantly more power from the ASIC, however, and the AC termination needs to closely match the frequency and rise time of the terminated signal. Therefore, in practice, parallel termination will rarely be possible.

- 4. If the total trace length is one rise time propagation delay or longer in length, follow standard high-speed design practices to minimize cross talk between the clock and the data signals.

Be aware that as the fabrication process for your ASIC improves, your output

Chapter 1: Target System Design Considerations Printed-Circuit Board Design Guidelines

driver will probably improve and your rise and fall times decrease. If you are close to violating the requirements of point 1, consider adding termination to the signals to ensure continued correct operation.

**NOTE:** Note that ASIC output pads which have an output impedance that is matched to the printed-circuit board trace may be available from your ASIC vendor. If these can be used, the signal quality of the trace port signals will be significantly improved.

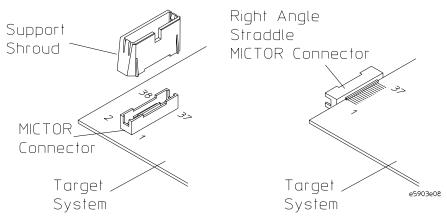

# Header Connector Requirements

The target system header connector is an AMP MICTOR (*Matched Impedance ConnecTOR*) which has a 0.64mm (0.025") lead pitch. The header has 38 pins and is organized such that it can handle:

- 16 trace status port pins

- 1 trace clock pin

- 1 voltage reference pin

- 5 JTAG control pins

- 2 processor control pins

# **Recommended Orientation**

The recommended trace port connector orientation is displayed in the following diagram.

#### **Connector Orientation**

There are two choices for the target header: a vertical connector, and a right angle straddle mount connector.

NOTE:

The vertical connector is recommended because it can accommodate an optional support shroud that provides additional strain relief and thus greater reliability. The notch on the support shroud should be placed on the same side as the odd numbered pins on the MICTOR connector. The support shroud is highly recommended.

The straddle mount connector should be used when board real estate is at a premium and there is no room for the vertical connector. A support shroud is not available for use with the straddle mount connector.

# **Connector and Support Shroud Part Numbers**

The AMP part numbers for the MICTOR target headers are given below. These connectors may be purchased directly from AMP. Support shrouds and kits of five MICTOR connectors and support shrouds may be purchased from Agilent.

#### **AMP MICTOR Headers Available from AMP**

| AMP Part<br>Number | Description                                                                  |

|--------------------|------------------------------------------------------------------------------|

| 2-767004-2         | Vertical surface mount connector<br>Ground bus lead length 1.397 mm (0.055″) |

| 767054-1           | Vertical surface mount connector<br>Ground bus lead length 2.743 mm (0.108″) |

| 767061-1           | Vertical surface mount connector<br>Ground bus lead length 3.505 mm (0.138″) |

| 767044-1           | Horizontal straddle mount connector                                          |

#### Support Shrouds Available from Agilent

| Agilent Part<br>Number | Description                                                                              |

|------------------------|------------------------------------------------------------------------------------------|

| E5346-44701            | Vertical support shroud for PCB thickness up to 1.575 mm (0.062")                        |

| E5346-44704            | Vertical support shroud for PCB thickness<br>from 1.575 mm (0.062") to 3.175 mm (0.125") |

| E5346-44703            | Vertical support shroud for PCB thickness<br>from 3.175 mm (0.125") to 17.780 mm (0.70") |

| Agilent Part<br>Number | Description                                                                                             |

|------------------------|---------------------------------------------------------------------------------------------------------|

| E5346-68701            | Set of 5 MICTOR connectors and shrouds<br>For PCB thickness up to 1.575 mm (0.062″)                     |

| E5346-68700            | Set of 5 MICTOR connectors and shrouds<br>For PCB thickness from 1.575 mm (0.062″) to 3.175 mm (0.125″) |

Set of Five MICTOR Connectors and Five Support Shrouds Available from Agilent

## **Connector Dimensions**

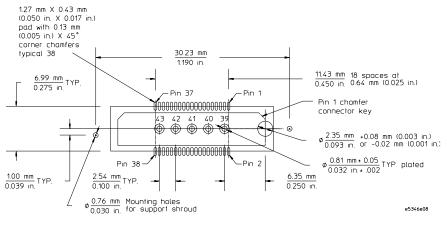

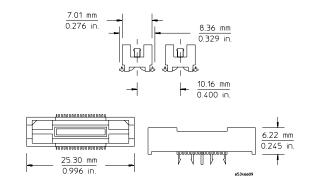

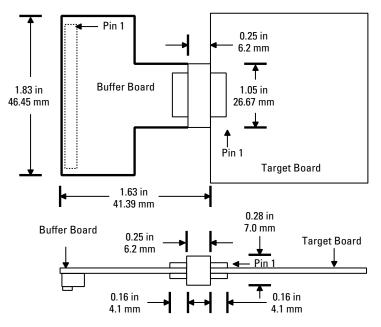

#### AMP MICTOR Connector Dimensions (AMP part # 2-767004-2)

# **Support Shroud Dimensions**

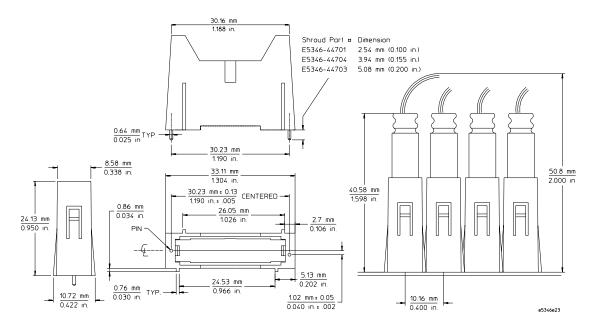

### **Support Shroud Dimensions**

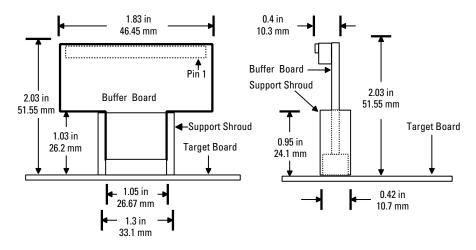

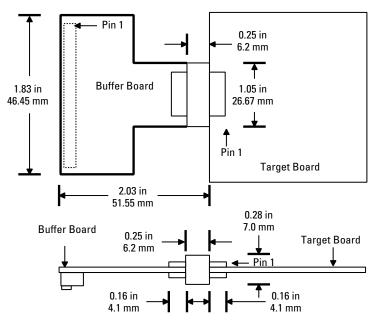

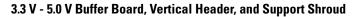

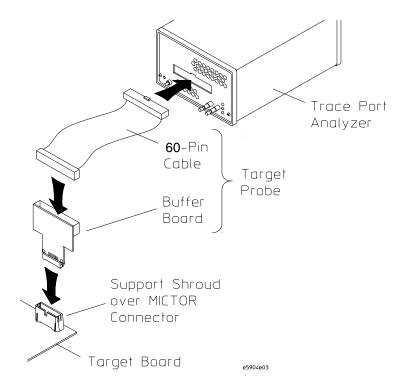

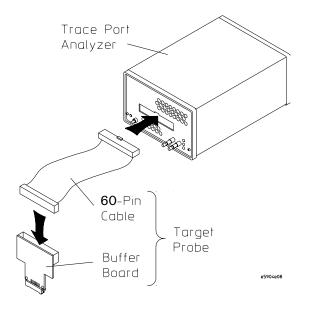

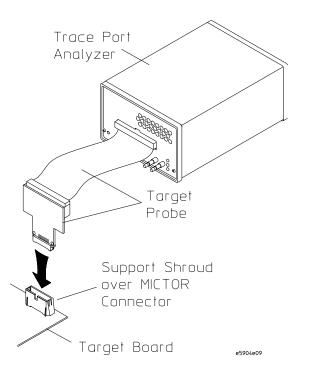

The Agilent Technologies E5904B Option 060 Trace Port Analyzer connects to the target MICTOR header with a small target probe (which consists of a 60-pin cable and a buffer board). The target probe connects either vertically or horizontally (to the edge of the target system PC board), depending on which MICTOR header you have installed on the target system.

If the vertical header is used, make sure there is sufficient height clearance between the target system and any interface boards.

This section describes the height restrictions and keep-out for two target probes:

- The 1.8 V 3.3 V buffer board (Agilent Part Number E5903-66503)

- The 3.3 V 5.0 V buffer board (Agilent Part Number E5903-66502)

**NOTE:** The numbers silkscreened on the buffer boards will differ from the part number by one digit. For example: the E5903-66503 will be marked E5903-26503.

# 1.8 V - 3.3 V Buffer Board, Vertical Header, and Support Shroud Agilent Part Number E5903-66503

#### Agilent Part Number E5903-66502

# **Target Header Connector Pin-Outs**

MICTOD

The PowerPC 4XX family trace port defines the following target header pinouts. If your target system has these pin-outs, use the included trace port analyzer buffer board.

### PPC/MPC 401<sup>†</sup>/403/405 Target Header Connector Pin-Out

|                      | MICTO<br>Connect |    |             |

|----------------------|------------------|----|-------------|

| TS6 (DATA)           | 38               | 37 | No Connect  |

| TS5 (DATA)           | 36               | 35 | No Connect  |

| TS4 (DATA)           | 34               | 33 | No Connect  |

| TS3 (DATA)           | 32               | 31 | No Connect  |

| TS2e (STATUS - EVEN) | 30               | 29 | No Connect  |

| TS1e (STATUS - EVEN) | 28               | 27 | No Connect  |

| TS2o (STATUS - ODD)  | 26               | 25 | No Connect  |

| TS1o (STATUS - ODD)  | 24               | 23 | No Connect  |

| No Connect           | 22               | 21 | nTRST       |

| No Connect           | 20               | 19 | TDI         |

| No Connect           | 18               | 17 | TMS         |

| No Connect           | 16               | 15 | ТСК         |

| No Connect           | 14               | 13 | No Connect  |

| Vref                 | 12               | 11 | TDO         |

| No Connect           | 10               | 9  | SRESET      |

| No Connect           | 8                | 7  | HALT        |

| TrcClk               | 6                | 5  | No Connect  |

| No Connect*          | 4                | 3  | No Connect* |

| No Connect*          | 2                | 1  | No Connect* |

#### Target Header Pin-Out for the MICTOR Connector

<sup>†</sup> When using the 401GF or the 401A1 (without the trace status port) do not connect TS[1:6] pins.

\* Pins 1, 2, 3, and 4 *must* be true no-connects; they are reserved for and may be driven by a logic analyzer.

### PPC/MPC 440 Target Header Connector Pin-Out

#### Target Header Pin-Out for the MICTOR Connector

| MICTOR<br>Connector |    |    |             |  |  |

|---------------------|----|----|-------------|--|--|

| TS6                 | 38 | 37 | ES3         |  |  |

| TS5                 | 36 | 35 | ES2         |  |  |

| TS4                 | 34 | 33 | ES1         |  |  |

| TS3                 | 32 | 31 | ES0         |  |  |

| TS2                 | 30 | 29 | BS2         |  |  |

| TS1                 | 28 | 27 | BS1         |  |  |

| TS0                 | 26 | 25 | BS0         |  |  |

| ES4                 | 24 | 23 | D0          |  |  |

| No Connect          | 22 | 21 | nTRST       |  |  |

| No Connect          | 20 | 19 | TDI         |  |  |

| No Connect          | 18 | 17 | TMS         |  |  |

| No Connect          | 16 | 15 | ТСК         |  |  |

| No Connect          | 14 | 13 | No Connect  |  |  |

| Vref                | 12 | 11 | TDO         |  |  |

| No Connect          | 10 | 9  | SRESET      |  |  |

| No Connect          | 8  | 7  | HALT        |  |  |

| TrcClk              | 6  | 5  | No Connect  |  |  |

| No Connect*         | 4  | 3  | No Connect* |  |  |

| No Connect*         | 2  | 1  | No Connect* |  |  |

NOTE:

\* Pins 1, 2, 3, and 4 *must* be true no-connects; they are reserved for and may be driven by a logic analyzer.

# Timing and Voltage Specifications for Trace Port Signals

The signals from the target system to the trace port analyzer must meet certain timing and voltage requirements in order for the Agilent Technologies E5904B Option 060 Trace Port Analyzer to work correctly.

# **Signal Requirements**

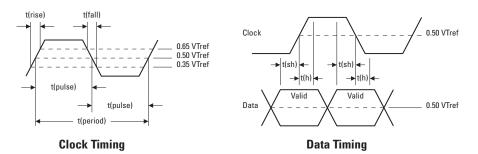

#### **Signal Requirements**

| Maximum state clock frequency<br>t(period) = 1/frequency   | 200 MHz (1.65 Volts to 3.6 Volts Target<br>VTRef)<br>5 ns |

|------------------------------------------------------------|-----------------------------------------------------------|

| Minimum clock pulse width, t(pulse)                        | 2 ns (see note 1)                                         |

| Maximum clock/data rise and fall time, t(rise) and t(fall) | 3.6 ns (see note 1)                                       |

| Minimum clock/data rise and fall time                      | See PCB guidelines                                        |

| Data setup/hold times, t(su)/t(h)                          | 1.5/1.0 ns (see notes 2 and 3)                            |

| NOTES:                                                     |                                                           |

1. Clock/data rise and fall times are measured between 35% and 65% of Target VTRef or +/- 30% of programmed threshold.

2. Setup/hold is measured at Target VTRef/2.

3. For "both edge" clocking, setup/hold must be met for both rising and falling edge of clock.

# **Required Voltage Levels: 1.8 V - 3.3 V Buffer** Board

| Absolute Maximum Ratings           | Minimum | Maximum            |

|------------------------------------|---------|--------------------|

| Target VT <sub>Ref</sub>           | -0.5 V  | 4.6 V <sup>1</sup> |

| Clock and Data                     | -0.5 V  | 4.6 V <sup>1</sup> |

| Input Current<br>(Input < -0.05 V) |         | -50 mA             |

<sup>1</sup> Minimum voltage can be exceeded if maximum current rating is observed.

| <b>Recommended Operating Range</b> | Minimum                | Maximum |

|------------------------------------|------------------------|---------|

| Target VT <sub>Ref</sub>           | 1.65 V                 | 3.6 V   |

| Clock and Data                     | 0.0 V                  | 3.6 V   |

|                                    |                        |         |

| DC Electrical Characteristics      | Minimum                | Maximum |

| Target VT <sub>Ref</sub> range     | 1.65 V                 | 3.6 V   |

| V <sub>ih</sub>                    | 0.65 VT <sub>Ref</sub> |         |

$V_{il}$

0.35 VT<sub>Ref</sub>

# Required Voltage Levels: 3.3 V - 5.5 V Buffer Board

| Absolute Maximum Ratings           | Minimum | Maximum |

|------------------------------------|---------|---------|

| Target VT <sub>Ref</sub>           | -0.5 V  | 5.5 V   |

| Clock and Data                     | -0.5 V  | 7.0 V   |

| Input Current<br>(Input < -0.05 V) |         | -50 mA  |

| Recommended Operating Range | Minimum | Maximum |

|-----------------------------|---------|---------|

| Target VT <sub>Ref</sub>    | 2.3 V   | 5.5 V   |

| Clock and Data              | 0.0 V   | 5.5 V   |

| DC Electrical Characteristics                        | Minimum | Maximum |

|------------------------------------------------------|---------|---------|

| Target VT <sub>Ref</sub> range                       | 2.3 V   | 5.5 V   |

| $V_{ih}$ (VT <sub>Ref</sub> = 2.3 V to 2.7 V)        | 1.7 V   |         |

| V <sub>ih</sub> (VT <sub>Ref</sub> = 2.7 V to 5.5 V) | 2.0 V   |         |

| $V_{il}$ (VT <sub>Ref</sub> = 2.3 V to 2.7 V)        | -0.5 V  | 0.7 V   |

| V <sub>il</sub> (VT <sub>Ref</sub> = 2.7 V to 5.5 V) | -0.5 V  | 0.8 V   |

# Loading Effects

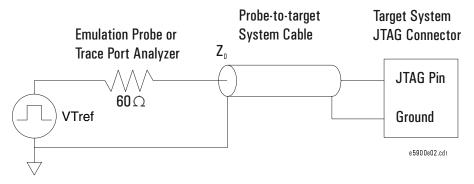

Target systems connect to the trace port analyzer via the target probe as shown below:

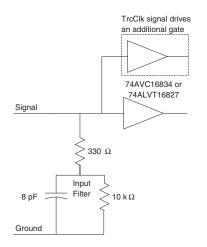

# Target Probe Equivalent Load

The trace port analyzer presents the following equivalent load to each signal. Target systems must be capable of driving this load and meeting the signal requirements given on page 30.

#### Trace Port Analyzer Buffer Board—Equivalent Load Model

| Buffer Board                 | Gate driven by target system |

|------------------------------|------------------------------|

| E5903-66503 (1.8 V to 3.3 V) | 74AVC16834                   |

| E5903-66502 (3.3 V to 5.0 V) | 74ALVT16827                  |

| Input resistance (DC)          | 10 kΩ ± 5% |

|--------------------------------|------------|

| Input capacitance, data inputs | 4.0 pF     |

| Input capacitance, clock input | 6.5 pF     |

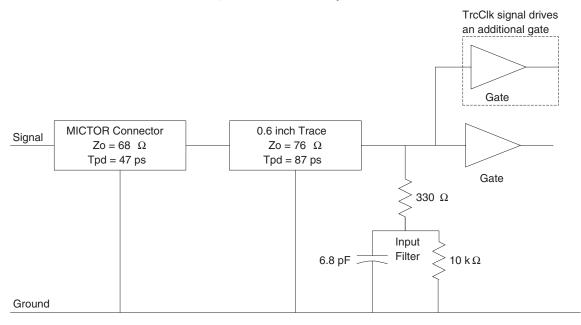

# Modeling the Trace Port Analyzer Buffer Board

The following characteristics apply to both the 1.8 V - 3.3 V buffer board (Agilent Part Number E5903-66503) and the 3.3 V - 5.0 V buffer board (Agilent Part Number E5903-66502).

### **MICTOR Connector**

• The MICTOR connector (right-angle plug to right-angle receptacle or right-angle plug to vertical receptacle) can be modeled as a transmission line with  $Z = 68 \Omega$  and Tpd = 47 ps.

### **PC Board**

- The trace port analyzer buffer board has the following characteristics:

- trace width = 0.127 mm (0.005 inches)

- trace thickness = 0.0178 mm (0.0007 inches)

- microstrip trace for TS, ES, BS, D0, and TrcClk signals

- distance from traces to ground plane = 0.178 mm (0.007 inches)

- spacing between traces = 0.508 mm (0.020 inches)

- ground plane thickness = 0.0356 mm (0.0014 inches)

- trace length = 15.24 mm (0.6 inches)

- Er = 4.8

- or

- $Zo = 76 \Omega$ , Tpd = 87 ps

### **Input Filter**

In place of the buffer board characteristics, you can use discrete models of 330  $\Omega$ , 6.8 pF, and 10 k $\Omega$  as shown below.

### **Undershoot/Overshoot**

Undershoot and overshoot at the inputs to the buffer IC must be within the absolute maximum ratings shown in the tables on pages 31 and 32.

Chapter 1: Target System Design Considerations Loading Effects

### Buffer IC-1.8 V to 3.3 V Buffer Board

Use the IBIS model of a Philips 74AVC16834 IC in a TSSOP package. This model can be found on the Philips Semiconductor web site at:

```

http://www.philipslogic.com/support/ibis/avc/

```

The clock signal (TrcClk) is connected to two inputs of the buffer IC. Data signals are only connected to one input of the buffer IC.

### Buffer IC-3.3 V to 5.0 V Buffer Board

Use the IBIS model of a Philips 74ALVT16827 IC in a TSSOP package. This model can be found on the Philips Semiconductor web site at:

```

http://www.philipslogic.com/support/ibis/alvt/

```

The clock signal (TrcClk) is connected to two inputs of the buffer IC. Data signals are only connected to one input of the buffer IC.

# Simplified Buffer Board Model

The following simplified discrete model of 330  $\Omega$ , 8 pF, 10 k $\Omega$ , and the gate (74AVC16834 for the 1.8 V - 3.3 V buffer board, or 74ALVT16827 for the 3.3 V - 5.0 V buffer board) can be used in place of the model previously presented.

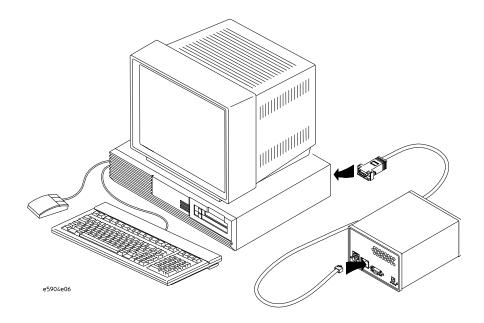

Connecting to a Power Source

|          | To connect the power supply                                                                                                                                                                                                                                                                                       |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | The trace port analyzer is shipped from the factory with a power supply and cord appropriate for your country. If the cord you received is not appropriate for your electrical power outlet type, contact your Agilent Technologies sales and service office (see "Contacting Agilent Technologies" on page 120). |

| WARNING: | Use only the supplied Agilent Technologies F1044B power supply and cord.<br>Failure to use the proper power supply could result in electric shock.                                                                                                                                                                |

| CAUTION: | Use only the supplied Agilent power supply and cord. Failure to use the proper power supply could result in equipment damage.                                                                                                                                                                                     |

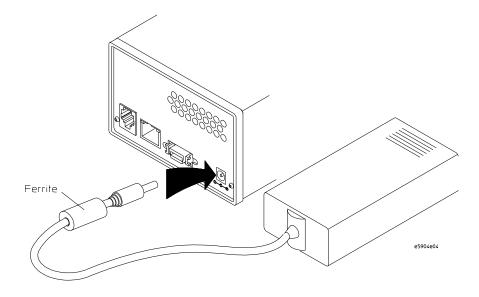

| 1        | Install the ferrite on the 12V power cord, near the end which plugs into the trace port analyzer.                                                                                                                                                                                                                 |

| 2        | Connect the power cord to the power supply and to a socket outlet.                                                                                                                                                                                                                                                |

|          |                                                                                                                                                                                                                                                                                                                   |

|          |                                                                                                                                                                                                                                                                                                                   |

|          | 23/3606                                                                                                                                                                                                                                                                                                           |

**3** Connect the 12V power cord to the back of the trace port analyzer.

Ensure the power supply plug is completely seated in the power input receptacle.

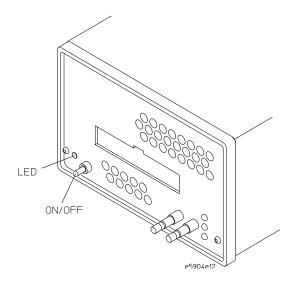

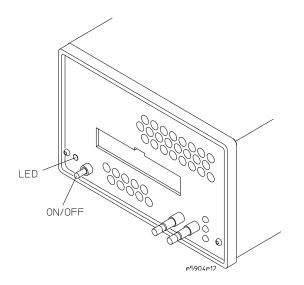

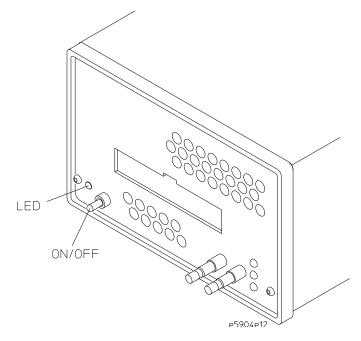

#### To turn power ON

This procedure is for the trace port analyzer before it has been connected to a target system. (For the power ON procedure when connecting to a target system, see Chapter 6, "Connecting to a Target System," on page 85.)

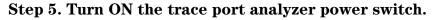

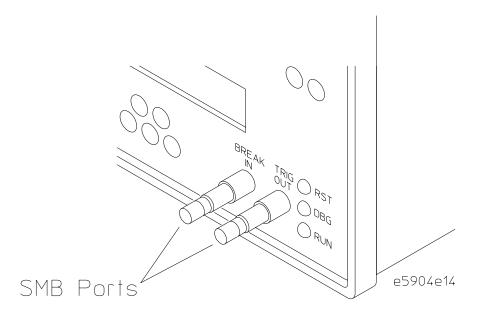

**1** Turn ON the trace port analyzer power switch.

#### To turn power OFF

This procedure is for the trace port analyzer before it has been connected to a target system. (For the power OFF procedure when connected to a target system, see Chapter 6, "Connecting to a Target System," on page 85.)

1 Turn OFF the trace port analyzer power switch.

Connecting to a LAN

|       | The trace port analyzer must be connected to the LAN and set up with the proper LAN parameters so that a debugger can communicate with it.                                                                                                                                       |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|       | The trace port analyzer has an IEEE 802.3 Type 10/100Base-TX LAN connector and is compatible with both 10 Mbps (10BASE-T) and 100 Mbps (100BASE-TX) twisted-pair ethernet LANs. (The trace port analyzer automatically negotiates the data rate for the LAN it is connected to.) |  |

| NOTE: | If the trace port analyzer is already active on the LAN and you wish to change<br>its LAN parameters, you can use a "telnet" command on a networked<br>computer to connect to the trace port analyzer; then, use the built-in "lan"<br>command to change LAN parameters.         |  |

| _     | After making LAN parameter changes, you must cycle power to the trace port<br>analyzer before the changes take effect. Doing this will break the network<br>connection and end the telnet session.                                                                               |  |

\_

## Step 1. Decide on the LAN setup method

The trace port analyzer can be set up on the LAN (in other words, its LAN parameters can be configured) in two ways:

- By a DHCP (Dynamic Host Configuration Protocol) server that responds to BOOTP requests.

- By using a computer with terminal emulation software (or by using an actual terminal) connected to the trace port analyzer's serial (RS-232) port, and by entering commands to set the LAN parameters.

## What is DHCP?

DHCP (Dynamic Host Configuration Protocol) allows clients (like the trace port analyzer) to obtain LAN parameters automatically from a server.

### How does the trace port analyzer use DHCP?

The trace port analyzer uses "static allocation" (sometimes called "manual allocation") to obtain a permanent IP address. Every time the trace port analyzer is turned on, it sends out a BOOTP request packet. If the DHCP server on the network responds to BOOTP requests and has been configured to reply to the trace port analyzer's link-level address, it will respond with the IP address and other LAN parameters.

The trace port analyzer does not support "automatic allocation", which permanently allocates IP addresses from a pool of addresses.

Nor does the trace port analyzer support "dynamic allocation" of IP addresses—it does not track lease duration and request a new IP address when the lease is about to expire.

# How does DHCP interact with other methods of setting LAN parameters?

Every time the trace port analyzer is turned ON, it sends out a BOOTP request packet (even if the LAN parameters have already been configured). As long as the DHCP server is configured to reply to BOOTP requests from the trace port analyzer's link-level address, it will respond with the IP address and other LAN parameters.

# Step 2. Set the trace port analyzer's LAN parameters

• Find out whether port numbers 6470 and 6471 are already in use on your network and if that use constitutes a conflict.

Computers on the network (running debugger software) communicate with the trace port analyzer through two TCP service ports. The default base port number is 6470. The second port has the next higher number (default 6471).

In almost all cases, the default numbers (6470, 6471) can be used without change. If necessary, the base port number LAN parameter can be changed (using a serial port connection) if the port numbers conflict with some other product on your network.

#### To set LAN parameters using DHCP

If there is a DHCP server on your network which responds to BOOTP requests and supports "static allocation" of IP addresses, it can be used to set the trace port analyzer's LAN parameters.

• Ask your system administrator to set up the IP address and other LAN parameters for the trace port analyzer on the DHCP server.

You will need to supply the link-level address of the trace port analyzer.

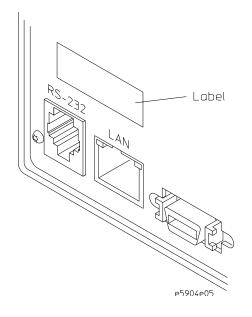

The link-level address (LLA) is printed on a label above the LAN connector on the trace port analyzer. This address is configured in each trace port analyzer shipped from the factory and cannot be changed.

#### To set LAN parameters using a serial port connection

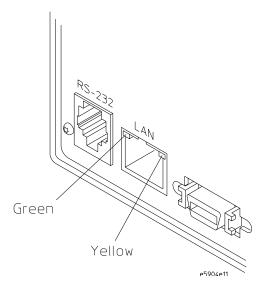

The Agilent Technologies trace port analyzer has a 9600 baud RS-232 serial interface with an RJ12 connector.

The trace port analyzer is shipped with a serial cable (with RJ-12 connectors on both ends, with 6-wire straight-through connections) and an adapter (female RJ-12 to female 9-pin D subminiature). The adapter plugs into 9-pin serial ports found on most PCs.

#### Serial connections on a workstation

If you are using a UNIX® workstation as the host computer, you need to use a serial device file. If a serial device file does not already exist on your host, you need to create one. Once it exists, you need to ensure that it has the appropriate permissions so that you can access it. See the system documentation for your workstation for help with setting up a serial device.

#### Serial connections on a personal computer

Serial connections are supported on personal computers. (You must use

## Chapter 3: Connecting to a LAN Step 2. Set the trace port analyzer's LAN parameters

hardware handshaking if you will use the serial connection for anything other than setting LAN parameters.)

If you are using a personal computer as the host computer, you do not need to set up any special files.

- **1** Get the following information from your local network administrator or system administrator:

- An IP address for the trace port analyzer.

You can also use a "LAN name" or "hostname" for the trace port analyzer, but you must configure it using the integer dot notation (such as 127.0.0.1).

• The gateway address.

The gateway address is an IP address and is entered in integer dot notation. The default gateway address is 0.0.0.0, which allows connections only on the local network or subnet. If connections are to be made to workstations on other networks or subnets, this address must be set to the address of the gateway machine.

• The subnet mask.

A subnet mask blocks out part of an IP address so that the networking software can determine whether the destination host is on a local or remote network. It is usually represented as decimal numbers separated by periods; for example, 255.255.248.0.

**2** Connect the serial cable from the host computer to the trace port analyzer.

Use the DB9-to-RJ12 adapter and the serial cable supplied with the trace port analyzer.

**3** Start a terminal emulator program on the host computer.

If you are using a personal computer, the HyperTerminal application in Microsoft Windows  $\ensuremath{\mathbbm W}$  will work fine.

If you are using a UNIX workstation, you can use a terminal emulator such as cu or kermit.

Chapter 3: Connecting to a LAN

Step 2. Set the trace port analyzer's LAN parameters

- ${\bf 4} \ \ {\rm Configure \ the \ terminal \ emulator \ program \ for:}$

- Communication rate: 9600 baud

- Data bits: 8

- Parity: none

- Stop bits: 1

- Flow control: none

- **5** Turn on power to the trace port analyzer.

When the trace port analyzer powers up, it sends a version message to the serial port, followed by a prompt.

6 Press the Return or Enter key a few times.

You should see a prompt such as "p>" or "R>".

If you don't see a prompt, refer to "If there are serial port connection problems".

For information about the commands you can use, enter "?" or "help" at the prompt.

7 Display the current LAN parameter settings by entering the lan command:

```

R>lan

lan is enabled

Link Status is UP

100BaseTX

lan -i 15.5.24.116

lan -g 15.5.23.1

lan -s 255.255.248.0

lan -p 6470

Ethernet Address : 08000909BAC1

R>

```

The Ethernet address, also known as the link level address, is preassigned at the factory, and is printed on a label on the trace port analyzer.

| 8                        | Change the LAN parameters by entering <b>lan</b> commands using the following syntax:                                                                                                                                                                                                                             |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | lan -i <internet> [-g <gateway>] [-p <port>] [-s<br/><subnet>]</subnet></port></gateway></internet>                                                                                                                                                                                                               |

|                          | The lan command parameters are:                                                                                                                                                                                                                                                                                   |

| -i <internet></internet> | The IP address which you obtained from your network administrator.                                                                                                                                                                                                                                                |

| -g <gateway></gateway>   | The gateway address. Setting the gateway address allows access outside your local network or subnet.                                                                                                                                                                                                              |

| -s <subnet></subnet>     | This changes the subnet mask.                                                                                                                                                                                                                                                                                     |

| -p <port></port>         | This changes the base TCP service port number, normally 6470.                                                                                                                                                                                                                                                     |

|                          | Do not change the default port numbers (6470, 6471) unless they conflict with<br>some other product on your network. The numbers must be greater than<br>1024. If you change the base port, enter the new value in the configuration of<br>your debugger (and, for UNIX workstations, in the /etc/services file). |

| Example                  | To assign an IP address of 192.6.94.2 to the trace port analyzer, enter the following command:                                                                                                                                                                                                                    |

|                          | R>lan -i 192.6.94.2                                                                                                                                                                                                                                                                                               |

#### If there are serial port connection problems

If the trace port analyzer prompt does not appear in the terminal emulator window (or terminal display) after pressing the Return or Enter key:

□ Make sure that you have connected the trace port analyzer to the proper power source and that the power switch is on.

With certain serial (RS-232) port interface cards, connecting to a serial port when the trace port analyzer is turned off (or is not connected) will hang the personal computer. The only way to get control back is to reboot the computer. Therefore, we recommend that you always turn on the trace port analyzer before attempting to connect via a serial port.

- □ Make sure the serial cable is connected to the correct serial port on your computer (or terminal).

- □ Make sure you are using the serial cable and adapter which are supplied with the trace port analyzer.

- □ Make sure that you have properly configured the terminal emulator (or terminal) data communications settings:

- Communication rate: 9600 baud

- Data bits: 8

- Parity: none

- Stop bits: 1

- Flow control: none

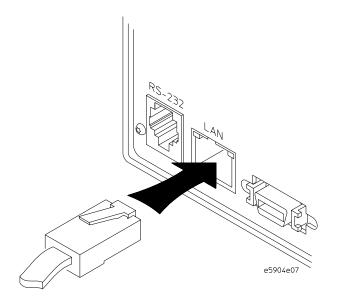

## Step 3. Connect the LAN cable

• Connect the LAN cable to the connector on the trace port analyzer.

Be sure to use the appropriate Category 3 or Category 5 cable for your LAN.

### Step 4. Cycle power on the trace port analyzer

**1** Cycle power on the trace port analyzer by powering it off then on again.

When using DHCP, you must cycle power in order for the trace port analyzer to send out a DHCPDISCOVER packet so that its LAN parameter settings can be set automatically by a server.

When using a serial connection, you must cycle power in order for the trace port analyzer's LAN parameter changes to take effect.

- **2** Wait at least 20 seconds for the trace port analyzer to recognize the LAN.

- **3** To verify that the trace port analyzer is now active and on the network, follow the instructions in the "Communicating with the Trace Port Analyzer" chapter.

**Entering Commands**

After the trace port analyzer has been connected to the LAN, there are two things you must do before you can configure the trace port analyzer:

- You must establish communications to the trace port analyzer from a networked computer.

- You must learn how to enter commands using the trace port analyzer's built-in command interface.

## Establishing Communications over the LAN

Once the trace port analyzer has been connected to the LAN, it can communicate with computers on the network.

#### To use debugger software

The Agilent Technologies trace port analyzer can be used with several third-party debuggers.

Debuggers typically provide some way to enter commands in the trace port analyzer's built-in command interface.

• Refer to your debugger's documentation for information on accessing the trace port analyzer's built-in command interface.

# If the debugger cannot communicate with the trace port analyzer

Some debuggers have an initialization file that needs to be properly defined before a debugger can connect to the trace port analyzer.

□ Check that the debugger is using the correct IP address for the trace port analyzer.

Refer to your debugger manual for information on specifying the trace port analyzer's IP address.

□ Telnet to the trace port analyzer from the same networked computer that runs the debugger software (see "To 'telnet' to the trace port analyzer").

If the telnet connection works, check that the debugger has the correct IP address for the trace port analyzer.

If the debugger uses the network *hostname* for the trace port analyzer (which doesn't work) and the telnet command uses the network *IP address* (which does work), the problem could be with the name server or host table lookup

## Chapter 4: Entering Commands Establishing Communications over the LAN

mechanism. If this is the case, try using the trace port analyzer's IP address in the debugger.

If the telnet connection doesn't work, refer to "Verifying Trace Port Analyzer LAN Communications" in the "Solving Problems" chapter.

|         | To "telnet" to the trace port analyzer                                                                                                                               |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Verify your trace port analyzer is now active and on the network by issuing a telnet command from a networked computer to the trace port analyzer's IP address.      |

| Example | \$ telnet 192.35.12.6<br>R><br>R>                                                                                                                                    |

|         | If you do not see a prompt, press the Return or Enter key a few times.                                                                                               |

|         | This connection will give you access to the trace port analyzer's built-in command interface.                                                                        |

| 2       | To enter a command, type it in at the built-in command interface prompt, and press the Return or Enter key.                                                          |

|         | For example, to view the LAN parameters, enter the "lan" command.                                                                                                    |

| Example | <pre>R&gt;lan lan is enabled Link Status is UP 10BaseT lan -i 130.29.66.134 lan -g 130.29.64.1 lan -s 255.255.248.0 lan -p 6470 Ethernet Address: 0030D300A10C</pre> |

${\bf 3}~$  To exit from the telnet session, type Ctrl+D at the prompt.

### If you cannot "telnet" to the trace port analyzer

Refer to "Verifying Trace Port Analyzer LAN Communications" on page 106.

# Using the Trace Port Analyzer's Built-In Commands

The trace port analyzer has a built-in command interface which you can use for configuring or troubleshooting the trace port analyzer.

You can access the built-in command interface via:

- A telnet (LAN) connection.

- A "debugger command" window in your debugger.

- A serial connection (as may have been used in "To set LAN parameters using a serial port connection" on page 45).

#### **Command Prompts**

The prompt indicates the status of the trace port analyzer:

| U | Running user program      |

|---|---------------------------|

| М | Running in debug mode     |

| р | No target power           |

| R | Trace port analyzer reset |

| r | Target reset              |

| ? | Unknown state             |

| x | Run control disabled      |

#### **Commonly Used Commands**

| Command | Description                                                                                                                |

|---------|----------------------------------------------------------------------------------------------------------------------------|

| b       | Break—go into the background monitor state.                                                                                |

| cf      | Configuration—read or write configuration options.                                                                         |

| help    | Help—display online help for built-in commands                                                                             |

| init    | Initialize—init -c re-initializes everything in the trace port analyzer except for the LAN software. ? init shows options. |

| lan     | Configure LAN parameters.                                                                                                  |

| m       | Memory—read or write memory.                                                                                               |

| reg     | Register—read or write a register.                                                                                         |

| mtest   | Memory test—test target system memory.                                                                                     |

| r       | Run—start running user code.                                                                                               |

| rep     | Repeat—repeat a command or group of commands.                                                                              |

| rst     | Reset—reset the target processor.                                                                                          |

| S       | Step—do a low-level single step.                                                                                           |

| ver     | Version—display the product number and firmware version of the trace port analyzer.                                        |

Use ? <command> (or help <command>) to show the command syntax and required parameters for each command. For example, enter ? mtest to show syntax and required parameters for the memory test command.

Chapter 4: Entering Commands Using the Trace Port Analyzer's Built-In Commands

#### Examples

To reset the trace port analyzer and break into the monitor, enter:

```

R>rst -m

```

To set register r0, and then view r0 to verify that it was set, enter:

M>reg r0=ffff

M>reg r0

reg r0=0000ffff

To break execution and then step a single instruction, enter:

```

M>b

M>s

PC=xxxxxxx

M>

```

To determine what firmware version is installed in the trace port analyzer, enter:

M > ver

#### **Online Help**

Use help *command name* to see the command syntax.

Example To get help on the memory command, enter: M>help m m - display or modify processor memory space m <addr> - display memory at address - display memory at address with display size m -d<size> <addr> - display memory at address using access size m -a<size> <addr> m <addr>..<addr> - display memory in specified address range m <addr>.. - display 128 byte block starting at address A - modify memory at address to <value> m <addr>=<value> m -d<size> <addr>=<value> modify memory with display size m -a<size> <addr>=<value> - modify memory using access size m <addr>=<value>,<value> - modify memory to data sequence

m <addr>..<addr>=<value>,<value> - fill range with repeating sequence NOTES: For display and access size descriptions see mo command

> Note that some of commands listed in the help screens are generic commands and may not be available for your trace port analyzer.

Configuring the Trace Port Analyzer

#### Chapter 5: Configuring the Trace Port Analyzer

After you have established communication between the trace port analyzer and networked computer (using a debugger or telnet software) and you've learned how to enter commands, you must set the trace port analyzer's configuration options appropriately for the target system.

You can save trace port analyzer configuration settings to a file so they can be used to re-configure the trace port analyzer at the beginning of each debugger session.

|         | Using the Built-In "cf" Command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | You can configure the trace port analyzer using the built-in "cf" commands.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | <b>1</b> Establish communications with the trace port analyzer over the LAN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | You can either telnet from a networked computer or you can use the debugger. For more information, refer to "Establishing Communications over the LAN" on page 55.                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         | Debuggers typically provide some way to enter commands in the trace port<br>analyzer's built-in command interface, or they provide a window for<br>configuring the trace port analyzer.                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | 2 Enter the built-in "cf" commands to view the current configuration settings.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Example | M>cf speed<br>cf speed=12MHz<br>M>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         | <b>3</b> Enter the "help cf" or "? cf" command to see a complete list of the configuration items that may be set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Example | p>? cf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|         | cf - display or set emulation configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | cf - display current settings for all config items<br>cf <item> - display current setting for specified <item><br/>cf <item>=<value> - set new <value> for specified <item><br/>cf <item>=<value> <item> - set and display can be combined</item></value></item></item></value></value></item></item></item>                                                                                                                                                                                                                                                                                     |

|         | help cf <item> - display long help for specified <item></item></item>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | VALID CONFIGURATION <item> NAMES<br/>rrt - Restrict to real-time runs<br/>reset - Configure reset actions<br/>speed - Set JTAG clock<br/>frztmrs - Select freeze timers option<br/>addrv - Enable address validation<br/>mrdop - Configure mem read operation<br/>dmwrop - Configure D mem write operation<br/>imwrop - Configure I mem write operation<br/>brfold - Enable branch folding<br/>breakin - Select SMB break input option<br/>trigout - Select SMB trigger output option<br/>fastload - Enable fast memory loads<br/>vref - Voltage reference<br/>thresh - Voltage threshold</item> |

Chapter 5: Configuring the Trace Port Analyzer Using the Built-In "cf" Command

**4** To see a more detailed description of any configuration item, use the command "help cf <item>".

| Example  | -<br>M>help cf rrt                                                                                                                                        |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Set restriction to real time runs                                                                                                                         |

|          | cf rrt=no - (default)                                                                                                                                     |

|          | This option does not restrict to real time and will break into background temporarily if needed.                                                          |

|          | cf rrt=yes                                                                                                                                                |

|          | This option restricts runs to real time which causes any command<br>that requires a break to the monitor to be rejected except 'rst',<br>'b', 'r' or 's'. |

| 5        | Use the <b>cf</b> commands to change the configuration settings (see "Setting the Configuration Options" on page 65).                                     |

| See Also | For information on other built-in commands, see "Commonly Used Commands" on page 59.                                                                      |

## Setting the Configuration Options

The configuration items must be set appropriately for each target system.

#### To specify whether runs are restricted to real-time

| Value | Meaning                                                                                                                                                                                                                | Built-in command |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| no    | Allows commands which break to the monitor.<br>Examples include commands which display<br>memory or registers. These commands break<br>to the monitor to access the target processor,<br>then resume the user program. | cf rrt=no        |

| yes   | No commands are allowed which break to the<br>monitor, except "break," "reset," "run," or<br>"step." The processor must be explicitly<br>stopped before these commands can be<br>performed. ( <b>Default</b> )         | cf rrt=yes       |

If your debugger allows displaying or modifying memory or registers while the processor is running, you must set "rrt=no" in order to use this feature.

#### To specify the reset behavior

The reset configuration item controls what happens when a reset occurs.

| Value | Meaning                                                                                                                                                                                                                                                                                                                                                                                                    | Built-in command |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| core  | A core reset resets the processor core, including<br>the data and instruction caches. It does not alter<br>the DMA controller, Bus Interface Unit or serial<br>port (if one exists). The content of external DRAM<br>is preserved since refreshes continue during<br>reset. Device Control Registers (DCRs) are not<br>affected by a core reset. A core reset stops the<br>processor at address 0xFFFFFFC. | cf reset=core    |

| chip  | A chip reset resets the entire chip including the<br>core, caches, DMA Controller, Bus Interface Unit<br>and serial port (if one exists). The content of<br>external DRAM is not preserved since refreshes<br>stop during and after the reset. A chip reset stops<br>the processor at address 0xFFFFFFFC. ( <b>Default</b> )                                                                               | cf reset=chip    |

| sys   | A sys reset resets the entire chip with the same<br>effect as a chip reset. In addition, the RESET signal<br>is driven active (low) for a minimum of three clock<br>cycles. A sys reset runs the processor from<br>address 0xFFFFFFC.                                                                                                                                                                      | cf reset=sys     |

| jtag  | A jtag reset merely resets the JTAG port on the processor. It does not affect any of the processor resources or its state.                                                                                                                                                                                                                                                                                 | cf reset=jtag    |

Note that these actions occur only when the RESET signal is not asserted. Using the built-in **rst** command asserts RESET continuously until another command causes RESET to be negated.

#### To specify the JTAG clock speed

The trace port analyzer must be configured to communicate at a rate that is compatible with your target system processor. The JTAG clock speed (on the TCK signal) is independent of processor clock speed.

| Value     | Built-in command       |

|-----------|------------------------|

| 11K - 50M | cf speed= <i>value</i> |

The speed value can be a number followed by either K, which indicates the value is in kHz; or M, which indicates the value is in MHz. The clock can be set to speeds in the range 11 kHz to 50 MHz. Not all values in this range are valid; if an invalid speed is entered, the next slower valid speed will be used.

#### Showing the current speed setting

Entering **cf speed** without a value will display the current JTAG clock speed. The default speed for the PowerPC 4XX trace port analyzer is 32 MHz.

#### Configuring the Debug Port for Maximum Performance